|

中星联华科技(北京)有限公司 |

|

FEC解决方案 |

|

应用文章 |

|

Derek Yin 2020-4-18

|

什么是FEC

关于FEC的权威定义,我们这里不妨借用一下Wiki上的描述:

“

在电信、信息论和编码理论中,前向纠错(Forward Error Correction ,简称FEC)或信道编码是一种用于在不可靠或有噪声的通信信道上控制数据传输错误的技术。中心思想是发送者以冗余的方式对消息进行编码,通常使用纠错码(Error Correction Code,简称ECC)。

冗余设计允许接收机检测到信息中出现的有限数量的错误,并且在不重新传输的情况下纠正这些错误。FEC使接收机能够在不需要数据重新传输的情况下纠正错误,但代价是固定的、更高的前向信道带宽。因此,FEC被应用于诸如单向通信链路等重传代价高昂或不可能的情况,以及向多个接收机发送数据时。例如,在围绕天王星运行的卫星上,由于解码错误而重新传输会造成5小时的延迟;FEC技术通常被用到大容量存储(基于磁、光和固态/闪存)设备中以恢复损坏的数据;FEC技术广泛应用于调制解调器中;FEC技术还可以用于主存储器为ECC存储器的系统和广播场合。

接收机中的FEC处理可应用于数字比特流或数字调制载波的解调。对于后者,FEC是接收机中模数转换的一个组成部分。Viterbi解码器实现了一种软判决算法,从被噪声污染的模拟信号中解调数字数据。许多FEC编码器还可以产生一个误码率(BER)信号,该信号可以作为反馈来微调模拟接收电子器件。

ECC的设计决定了可以校正的最大误码率或丢失比特率,因此不同的前向纠错码适用于不同的情况。一般来说,包含更多冗余的强编码方式,需要占用有效带宽来进行传输,在提高接收到信号的信噪比的同时会降低有效比特率。Shannon的噪声信道编码定理回答了这样一个问题:在使用将解码错误概率变为零的最有效的编码时,数据通信还剩下多少带宽。这就建立了在给定基本噪声水平下,信道的理论最大信息传输速率的极限。他的证明并不具有建设性,因此无法洞察如何构建可实现能力的代码。然而,经过多年的研究,一些先进的FEC系统如极性码在无限长帧的假设下获得了Shannon信道容量。

”

——《维基百科-Forward error correction》

到底哪里会用到FEC

了解了FEC的定义后,我们有了一个基本的概念,FEC是用来提升通信质量的,在有限带宽下如果要保障有效的高数据率传输就必须要用到FEC。但是到底生活中哪些不为人知的地方用到了FEC呢?

5G的速度可以达到1GB每秒,用的人一多,主干网怎么负担得起?想想你在农药战场正准备进行激烈的团战,坦克都已经进团嘲讽对面了,突然因为网络传输错误C位跟着闪现进去了,你是什么感受?不过也不用担心,早有人未雨绸缪。

(手机通信数据中断)

目前,全国正在推进新型基础设施建设,5G就是新基建七大领域之一。5G时代承载带宽需求的大幅度上升、网络扁平化、大型中心机房和数据中心的互联,将给骨干网提出巨大挑战,有专家认为,目前单波100G骨干网难以满足5G商用成熟之后的网络带宽需求。据工信部数据,2019年,移动互联网接入流量消费达1220亿GB,比上年增长71.6%。截至去年12月底,互联网宽带接入端口数量达到9.16亿个,其中光纤接入(FTTH/0)端口达到8.36亿个。工信部通信科技委常务副主任、中国电信集团公司科技委主任韦乐平预计,中国骨干网容量将在2020年突破1Pbps,2022年有望接近1.4Pbps。值得注意的是,有专家指出,骨干网正在向400G、600G演进,预计2021年1T设备成熟。

(通信数据量增长趋势图)

由于庞大的数据量导致链路容限接近饱和,数据中心和承载网络都具有超低时延的要求,这导致丢失数据无法再次重新传递,为了节省成本采用多电平传输的方式。4 Pulse Amplitude Modulation(简称PAM4)作为新出现的高速串行总线编码模式,在几乎所有的超过200G、400G的标准中都存在。 由于在同等速率的情况下带宽的要求是NRZ的一半,对于绝大多数的高速电缆,背板以及连接器而言,通过PAM4可以在速率增倍的情况下具备同样的奈奎斯特频率。

由于每一个symbol或者每一个UI传输2个比特的数据,也就是在同样的输出幅度的情况下,需要区分4 个不同的电平,这带来了9dB的信噪比恶化。在高速总线传输过程中,抖动和噪声是影响误码率的最关键指标,信噪比恶化意味着误码率的提升。所以在相同速率的情况下对比NRZ和PAM4,PAM4利用了4电平的调制方式通过牺牲信噪比来换取奈奎斯特频率的减半,也就是说 PAM4对传输带宽的要求减少了一半。下图是NRZ和PAM4 这2种编码模式下的带宽、速率、定时、信噪比的对比。

(NRZ和PAM4对比图)

虽然相同带宽下传输速率提高了,即便是以中星联华科技(北京)有限公司的SL3040A PAM4高速误码仪发送端的优越质量,在经过了传输通道后糟糕的信噪比会导致误码率超过容限。FEC技术可以有效降低数据传输误码率,具体可以降低到什么程度呢?我们以400G中 (53.125 Gbps每通道)为例:电信号的误码率要求在纠错前为1E-5/1E-6,而光信号为2.4 E-4,采用FEC纠错后误码率可以优于1E-15,由此可见FEC虽然增加了传输冗余却显著提高了数据的有效性。

(SL3040A 53.125Gbps发送端眼图)

FEC是如何实现的

FEC在发送端对信源信息进行一定形式的编码,如Hamming编码、Golay编码、BCH编码、Reed Solomon编码(简称RS编码),然后用新的编码流进行传输,在接收端再进行解码与纠错,光通信领域使用较多的编码形式以RS编码为主。

标准 RS(n,k) 标准协议 单通道速率

|

标准 |

RS(n,k) |

标准协议 |

单通道速率 |

|

100GBase-KR4 100GBase-CR4 |

RS(528,514) RS(544,514) |

IEEE 802.3bj |

25.78125Gbps NRZ |

|

200/400GBase |

RS(544,514) |

IEEE 802.3bs |

26.5625GBd PAM4 or NRZ 53.125Gd PAM4 or NRZ |

|

25GBase-KR 25GBase-CR |

RS(528,514) |

IEEE 802.3by |

25.78125GBd NRZ |

RS编码采用硬件可以实现的有限域运算实现,是一种交织编码,使用一组纠错码。与低密度校验码和turbo码相比,具有更小的编码增益。但是它有很高的编码速率并且复杂度低,所以它适用于许多应用场景。交织编码将可能出现的长串误码分散到多个RS编码序列中,使得分散后的误码长度落到编码纠错能力范围之内,从而使得交织处理之前超出纠错能力的长误码串也能得到正确的恢复。RS编码会将需要编码的流数据重新排列为以「符号(symbol)」为单位的数据块,所以采用RS编码的FEC纠正的是Symbol error而不是bit error。

(RS重新编码)

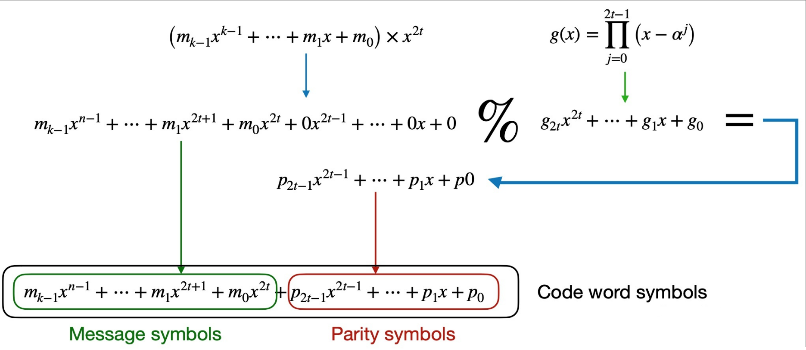

以RS(544,514,15,10)表示方式举例,每个符号Symbol数据位宽位10位(m=10bits),原始数据为514个符号(k=514),校验数据为30个Symbol(t=15),最终编码完成后符号总数为544个Symbol(n=544)。

IEEE 802.3中定义了编码的算法,编码的数学过程并不复杂。将原始64B/66B的codeword编码的数据后面补30个0,除以生成多项式 g(x)取余下的多项式为校验多项式p(x),将校验多项式加到刚才补过0的编码数据多项式中,就是最终生成的编码。

实际实现时将原始输入的64B/66B编码经过转码器对每四个通道的数据进行转码,(262比特到257比特) 从而减少编码开销。对转码后的数据进行加扰,以防止长时间运行0或1。将对齐游标插入到16条PCS通道。每条通道都有其各自唯一的游标。经过一个变速器(gearbox)给每514个比特增加30比特,为传输FEC校验和预留好位置。补充的冗余位数会在两个FEC编码引擎之间进行分配。分配结束后,任何突发误差都会由两个FEC引擎负责,从而提供了更好的纠错能力。FEC的编码交织处理后,数据会被分配给16个PCS通道。在PAM4系统中,每两个通道相互连接,形成8个50G通道。在接收方向上,情况恰好与此相反。

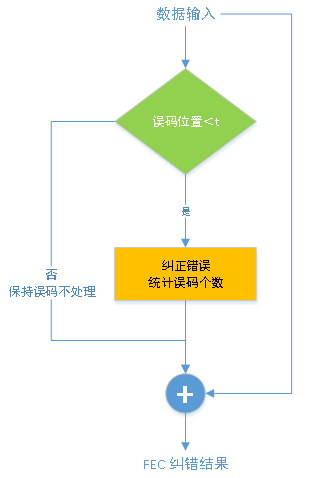

在RS ( 544, 514, 15, 10 )每一帧中最大可修正错误符号个数为15个,每一个symbol包含10bits。每一组编码中可以纠正15个Symbol,如果符号误差超过 15 个,就会导致编码无法被纠正。在 400GE 系统中,一个错误的编码将会导致大约 15 个 64B数据包丢失。

中星联华解决方案

通道数支持4/8通道;

每一个通道支持PAM4和NRZ任意切换;

支持22Gbaud-29.6Gbaud PAM4收发速率;

支持9Gbps到14Gbps、18-29.6Gbps NRZ收发速率;

速率步进1kbps;

上升下降时间:14ps(typ);

输出抖动: 28G输出下固有随机抖动Rj小于800fs;

PPG码型发生器最大输出幅度从0.5V/1000mV可选;

支持各种常用码型: prbs7/ 9/11/13/15/ 23/ 31, prbs7Q~31Q、SSPRQ、用户自定义码型;

误码仪输入灵敏度50mV;

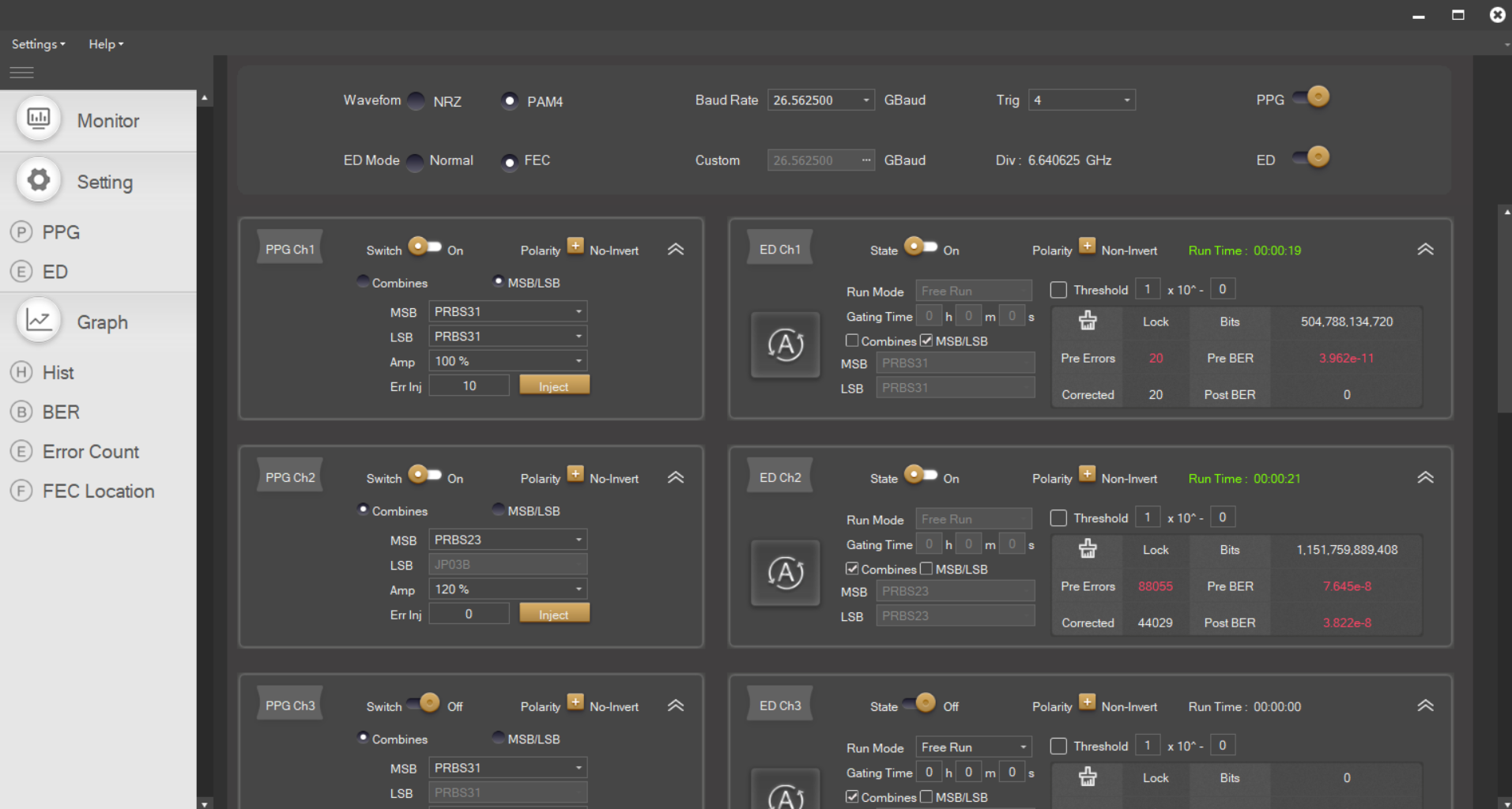

具备FEC 符号错误纠正功能,具有误码符号分布图,支持FEC-KR4和FEC-KP4

在软件界面上可以快速设置FEC模式,显示纠错前的误码个数和误码率、纠错后的误码个数和误码率,纠正的误码个数。具有接收端自动检测功能,可以自动匹配支持的码型并显示,可以自动纠正接收端极性,避免了使用过程中因错误链接带来的复杂操作。

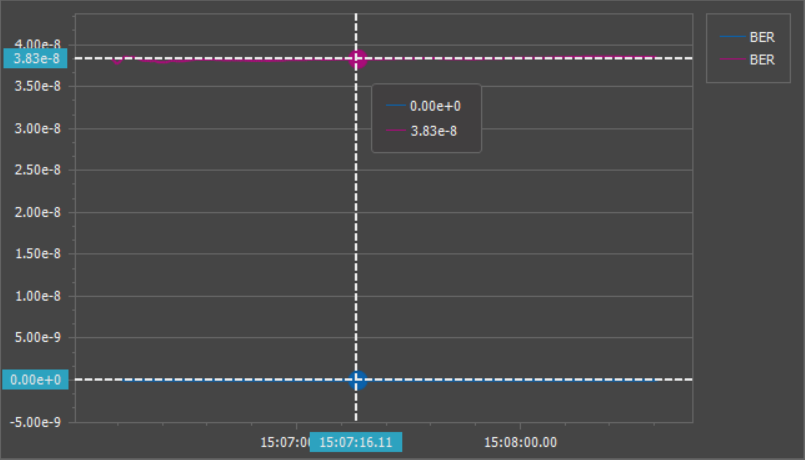

误码检测同时还能够检测误码个数和误码率曲线随时间的变化,进行无人值守任务时,能够有效定位到各个通道故障发生时间,为调试测试使用带来了极大便利。

同时能够监测不同通道的错误符号位置,通过柱状图能够有效判断系统FEC余量和误码分布状况。

产生误码时,还可以通过眼图等高线功能查看能量分布,通过图形可以直观判断接收端眼图的线性度、电平位置和信噪比等。

XBERT系列高速串行误码仪具有优异的性能指标、丰富的功能特点、灵活的选件配置和超高的整机集成度,为高速串行电路产品预研、设计和生产测试提供了强大的性能和灵活性保障。全系列产品具有速率1kbps连续可调的特点,有效的保证了测试的灵活性和全面性,可以有效测试被测电路的余量和极限参数。同时可编程码型发生器(PPG)能够提供多级去加重,补偿信号在传输过程中的损耗,改善信号质量。误码检测器(ED)内置了均衡电路,无需外接有源或无源的信号调理电路来保证链路的信号完整性,同时内置快速锁定的时钟恢复模块,保证了误码测试时链路的稳定性,使得误码检测器自身误码率小于10-15的严格要求,保证在恶劣复杂的测试环境中误码测试的准确性。